【UVC】UVC介绍

- 时间:2021-09-16作者:深圳市科电电子有限公司浏览:1174

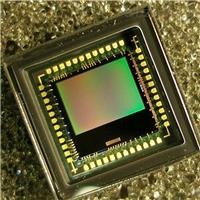

深圳市科电电子有限公司专注于FPGA厂家,sensor厂家,LDO厂家,UVC,储存快充芯片,环境光距离传感器等

词条

词条说明

FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为**集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA 器件属于**集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA 的基本结构包括可编程

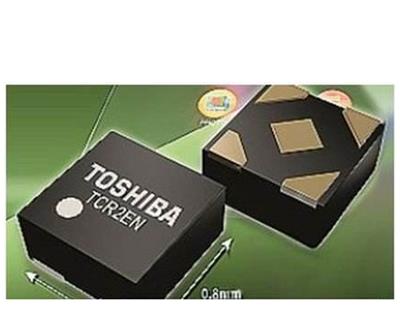

LDO 是一种线形稳压器。线性稳压器应用在其线形地区内运作的晶体管或 FET,从运用的键入电压中减掉**量的电压,造成通过调整的输出电压。说白了压降电压,就是指稳压器将输出电压保持在其额定电流左右 100mV 以内需要的键入电压与输出电压净额的较小值。正输出电压的LDO(低压降)稳压器通常应用输出功率晶体管(也称之为传送机器设备)做为 PNP。这类晶体管容许饱和状态,因此稳压器可以有一个较低的压降电

FPGA的优点如下: (1) FPGA由逻辑单元、RAM、乘法器等硬件资源组成,通过将这些硬件资源合理组织,可实现乘法器、寄存器、地址发生器等硬件电路。(2) FPGA可通过使用框图或者Verilog HDL来设计,从简单的门电路到FIR或者FFT电路。(3) FPGA可无限地重新编程,加载一个新的设计方案只需几百毫秒,利用重配置可以减少硬件的开销。(4) FPGA的工作频率由FPGA芯

LDO即low dropout regulator,是一种低压差线性稳压器。这是相对于传统的线性稳压器来说的。传统的线性稳压器,如78XX系列的芯片都要求输入电压要比输出电压至少高出2V~3V,否则就不能正常工作。但是在一些情况下,这样的条件显然是太苛刻了,如5V转3.3V,输入与输出之间的压差只有1.7v,显然这是不满足传统线性稳压器的工作条件的。针对这种情况,芯片制造商们才研发出了LDO类的电

联系方式 联系我时,请告知来自八方资源网!

公司名: 深圳市科电电子有限公司

联系人: 聂绍明

电 话: 13243662666

手 机: 13823729687

微 信: 13823729687

地 址: 广东深圳宝安区31区水口花园6片37号205

邮 编:

相关推荐

相关阅读

1、本信息由八方资源网用户发布,八方资源网不介入任何交易过程,请自行甄别其真实性及合法性;

2、跟进信息之前,请仔细核验对方资质,所有预付定金或付款至个人账户的行为,均存在诈骗风险,请提高警惕!

- 联系方式

- 相关企业

- 深圳市宇正芯科技有限公司

- 深圳市恒辰微电子有限公司

- 深圳市光达电子有限公司

- 四川芯毅光通信科技有限公司

- 深圳市岳邦电子科技有限公司

- 深圳市沃德一佳科技有限公司

- 深圳市悦为光电科技有限公司

- 深圳市鑫永诚光电科技有限公司

- 泉州市速冠电子科技有限公司

- 宁波市浩天电子有限公司

- 商家产品系列

- lcd液晶显示屏

- led灯

- led电源

- led配件

- led软灯条

- led元件

- pcb制作设备

- 红外线发射管

- 红外线接收头

- 霍尔传感器

- 霍尔开关

- 霍尔元件

- 机电元件

- 激光模组

- 激光器

- 激光头

- 记忆存储芯片

- 空心线圈

- 拉伸膜

- 锂电池

- 锂电池组

- 连接件

- 录音磁头

- 滤波器

- 铝电解电容器

- 铆接设备

- smt贴片机

- usb连接器

- 半导体材料

- 半导体设备

- 产品推荐

- 资讯推荐